Explanation of the Stress Tests

Combined Environment (Vibration Step Stress (RS Shaker) +Thermal Shock)

Stress Test Background

Combined environment (Thermal Shock and random vibration) is typically used for design improvement and stress screening purpose for electronic systems. It is usually used as the last stress after Cold, Hot Step Stress, Thermal Shock and Vibration Step Stress in HALT as the most severe stress condition in an attempt to catch the defects that escaped the previous stresses under the synergies of thermal cycling and vibration that resembles real life conditions. With test-unit specific stress levels, combined environment is used as a typical stress screening profile in ESS and HASS. Depending on the test purpose and different handbooks or standards being followed, there are modifications to the test profile and different requirements for the test facilities.

Random vibration generated with repetitive shock (RS) shakers is a typical requirement in HALT, HASS standards and guidelines, while both RS shakers and electrodynamic (ED) shakers are typically accepted in ESS standards and guidelines. Vibration from an RS shaker is one that originates from a repeated shock impulse excitation, typically created from pneumatic hammers impacting a vibration table to which test samples are attached. Compared to vibration from Electrodynamic (ED) shaker, RS shakers offer two main features that are beneficial for defect precipitation in electronics systems.

- Energy is focused on the higher frequency spectrum, which is more critical for testing smaller structures such as printed circuit boards and components.

- Simultaneous multi-axial vibration generates synergistic effects of all modes being excited and a more realistic vibration stress loading condition, which better approximates real world vibrations being experienced by products

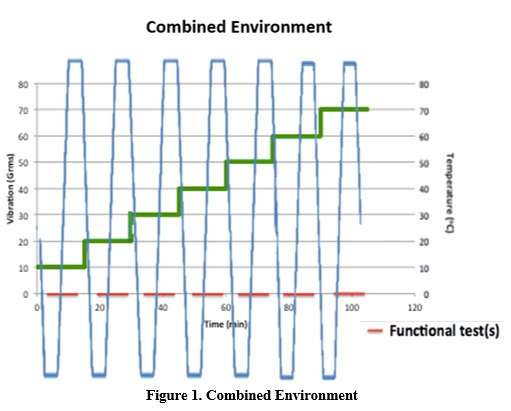

The stress profile shown in Figure 1 at the bottom resembles the test descriptions in IPC 9592A, IEST-RP-PR-003.1, and GMW 3172 for HALT. Apart from the ability in precipitating defects with the stress, detecting failures with functional tests, relationship between types of failures and discrete stress levels is also addressed in the profile design for proper corrective actions be made for the improvement in design margins.

Stress Profile Description

A typical profile used for design improvement is a superposition of vibration step stress and thermal shock. Vibration step stress typically start from 5 to 10 Grms, Then step up by fixed increments to the maximum acceleration level with sufficient dwell time at each step. For thermal shock, starting with room temperature, the temperature is then ramped between pre-defined minimum and maximum temperatures at a desired ramp rate for specific number of cycles. Functional tests are performed at each temperature step either at specific times or continually. The ability to detect failures will depend on the functional test coverage.

Parameters Determination

Step Size

Based upon the accuracy required for failure point definition and the time available for testing. Reduce step size as failure point is reached is appropriate, which allows a fine definition without compromising test duration.

Dwell time

For design improvement purposes (HALT), a longer dwell time can be appropriate for more defects to be precipitated and corrected for field robustness of the product. It is suggested to be at least 10 minutes in both IPC 9592A and GMW 8287.

For screening purposes (HASS, ESS), also depend on the stress limits being decided, remaining life of the good population should be taken into account when deciding dwell time.

Target stress level for thermal shock, Maximum acceleration level, Tmax, Tmin, Ramp Rate

For design improvement purposes (HALT), stress levels to be high enough to precipitate defects that can cause failures below the desired stress limits or before the desired lifetime. If used after Cold Step Stress and Hot Step Stress as in conventional HALT, the stress limits determined in these tests are often used for determination of Tmax and Tmin in Combined Environment. In HALT standards, Tmax and Tmin are typically set to be within 5 to 10°C of the upper and lower operating limits. Ramp rates are suggested to be at least 20°C/ min, at least 45 °C/ min, and maximum attainable ramp rate as recommended by IEST-RP-PR-003.1, IPC 9592A, and GMW 8287 respectively, convincingly due to the different scopes of products the standards cover.

For screening purposes (HASS, ESS), target stress levels should be set lower to allow for sufficient remaining lifetime of the population with less critical defects remain in the products. For HASS, it is suggested by the listed standards that the Tmax and Tmin should be 80 -85% of upper and lower operating limits found in HALT in combination with vibration during dwell times.

Target stress level for vibration step stress, Maximum acceleration level

For design improvement purposes (HALT), stress levels to be high enough to precipitate defects that can cause failures below the desired stress limits or before the desired lifetime. It is usually determined based on the destruct limit of the unit from the result vibration step stress or the vibration test limit of the chamber.

For screening purposes (HASS, ESS), target stress levels should be set lower to allow for sufficient remaining lifetime of the population with less critical defects remain in the products.

Number of Cycles

For design improvement purposes (HALT), higher number cycles can be appropriate for more defects to be precipitated and corrected for field robustness of the product.

For screening purposes (HASS, ESS), with stress limits also taken into account, remaining life of the good population should be considered when deciding number of cycles.

Standards with Stress Test Description

For Design Improvement Purpose

- IPC 9592A: Requirements for Power Conversion Devices for the Computer and Telecommunications Industries

- IEST RP PR 003.1: HALT and HASS

- GMW 8287: Highly Accelerated Life Testing (HALT) Highly Accelerated Stress Screening and Auditing

- MIL-HDBK 344A: Environmental Stress Screening (ESS) of Electronic Equipment

- MIL-HDBK 2164A: Environmental Stress Screening Process for Electronic Equipment

- IEST-RP-PR001.1: Management and Technical Guidelines for the ESS Process

- IEC-61163-1: Reliability Stress Screening

For Testing/ Acceptance Purpose

Typical Defects Precipitated by this Stress

|

Defect Location |

Typical Defects |

Failure Mechanism(s) |

|

Solder Joints |

Voids |

Mechanical Fatigue/ Overstress |

|

Cracks |

||

|

Cold Solder |

||

|

Insufficient Solder |

||

|

Corroded Solder |

||

|

Plated Through Holes (PTHs) |

Poor Hole Fill |

Mechanical Fatigue/ Overstress |

|

Glass Fiber Protrusion |

||

|

Irregular Plating |

||

|

Plating Voids |

||

|

Resin Smear |

||

|

Inner Plane Delamination |

||

|

Microvias |

Voids |

Mechanical Fatigue/ Overstress |

|

Poor Bonding of Pad/Via Interface |

||

|

Barrel/ Corner Cracks |

||

|

Metallizations |

Poor Adhesion of Surface Traces |

Mechanical Fatigue/ Overstress |

|

Internal Trace Delamination |

||

|

Connectors |

Irregular Press Fit Pins |

Mechanical Fatigue/ Overstress |

|

Corroded Contacts |

||

|

Dust Accumulation |

||

|

Loosened Contacts |

||

|

Passive Parts/ Integrated Circuits |

Distorted Leads |

Mechanical Fatigue/ Overstress |

|

Poor Solderabiltiy of Leads |

Top